- 您现在的位置:买卖IC网 > Sheet目录3769 > ATMEGA8515-16JUR (Atmel)MCU AVR 8KB FLASH 16MHZ 44PLCC

118

ATmega8515(L)

2512K–AVR–01/10

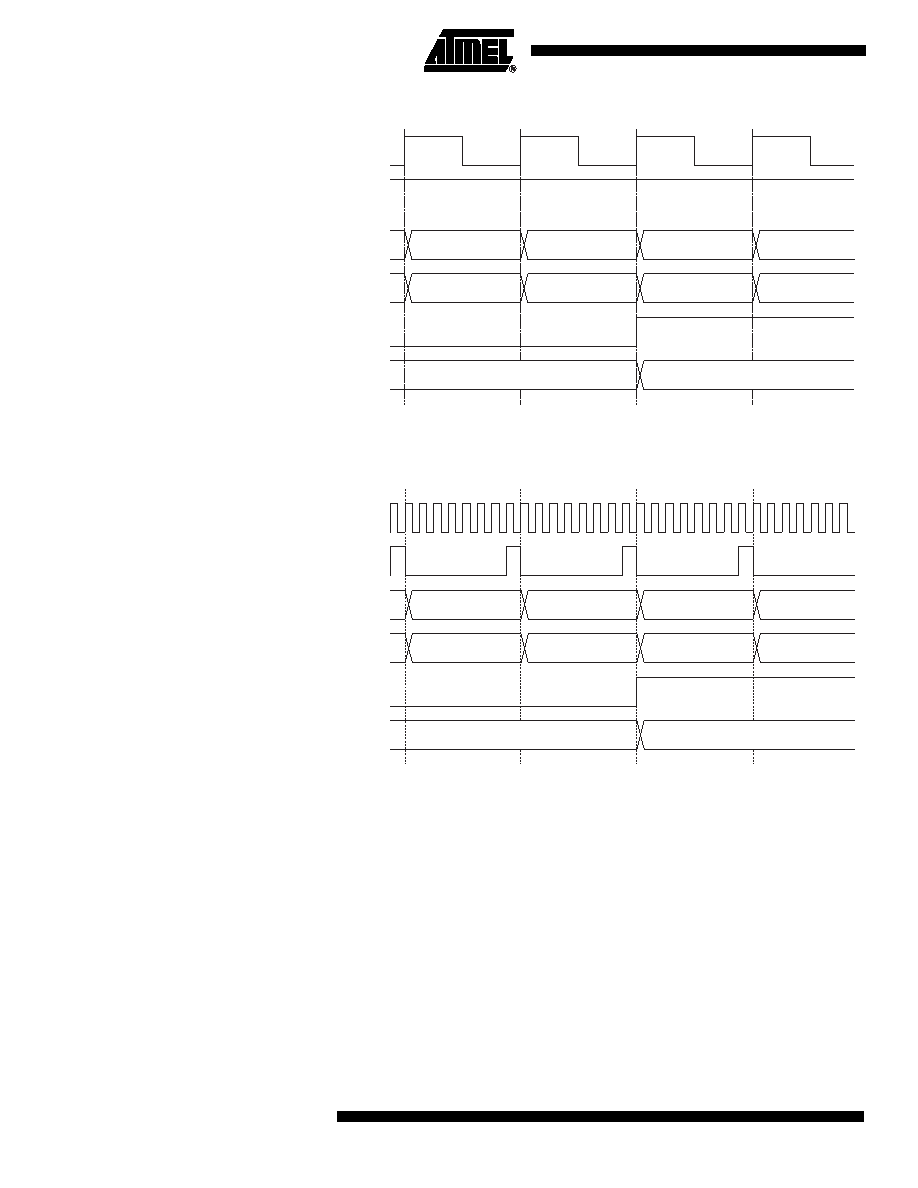

Figure 58. Timer/Counter Timing Diagram, No Prescaling

Figure 59 shows the same timing data, but with the prescaler enabled.

Figure 59. Timer/Counter Timing Diagram, with Prescaler (f

clk_I/O/8)

TOVn (FPWM)

and ICFn (if used

as TOP)

OCRnx

(Update at TOP)

TCNTn

(CTC and FPWM)

TCNTn

(PC and PFC PWM)

TOP - 1

TOP

TOP - 1

TOP - 2

Old OCRnx Value

New OCRnx Value

TOP - 1

TOP

BOTTOM

BOTTOM + 1

clk

Tn

(clk

I/O/1)

clk

I/O

TOVn (FPWM)

and ICFn (if used

as TOP)

OCRnx

(Update at TOP)

TCNTn

(CTC and FPWM)

TCNTn

(PC and PFC PWM)

TOP - 1

TOP

TOP - 1

TOP - 2

Old OCRnx Value

New OCRnx Value

TOP - 1

TOP

BOTTOM

BOTTOM + 1

clk

I/O

clk

Tn

(clk

I/O/8)

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PCA9555D/G-T

IC I/O EXPANDER I2C 16B 24SOIC

ATMEGA48-15AZV

MCU AVR 4K FLASH 15MHZ 32-TQFP

ATMEGA48-15AZ

MCU AVR 4K FLASH 15MHZ 32-TQFP

MIC74BQS

IC I/O EXPANDER I2C 8B 16QSOP

EXPANDIO-USB-PT-FS

IC I/O EXPANDER USB 32B 44TQFP

MAX7300ATL+

IC I/O EXPANDER 2WIRE 40TQFN

MAX7300ATL+T

IC I/O EXPANDER 2WIRE 40TQFN

MAX7300AAX+T

IC I/O EXPANDER I2C 28B 36SSOP

相关代理商/技术参数

ATmega8515-16MC

功能描述:8位微控制器 -MCU AVR 8K FLASH 512B EE SPI/UART/TWI 5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATmega8515-16MI

功能描述:8位微控制器 -MCU AVR 8K FLASH 512B EE SPI/UART/TWI 5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8515-16MJ

功能描述:IC MCU AVR 8K 5V 16MHZ 44-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:AVR® ATmega 标准包装:9 系列:87C 核心处理器:8051 芯体尺寸:8-位 速度:40/20MHz 连通性:UART/USART 外围设备:POR,WDT 输入/输出数:32 程序存储器容量:32KB(32K x 8) 程序存储器类型:OTP EEPROM 大小:- RAM 容量:256 x 8 电压 - 电源 (Vcc/Vdd):4.5 V ~ 5.5 V 数据转换器:- 振荡器型:内部 工作温度:0°C ~ 70°C 封装/外壳:40-DIP(0.600",15.24mm) 包装:管件

ATmega8515-16MU

功能描述:8位微控制器 -MCU AVR 8K FLASH 512B EE SPI/UART/TWI 5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8515-16MUR

功能描述:8位微控制器 -MCU AVR 8KB FLSH 512B EE 512B SRAM-16MHz, IND RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8515-16PC

功能描述:8位微控制器 -MCU AVR 8K FLASH 512B EE SPI/UART/TWI 5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATmega8515-16PI

功能描述:8位微控制器 -MCU AVR 8K FLASH 512B EE SPI/UART/TWI 5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8515-16PJ

功能描述:IC MCU AVR 8K 5V 16MHZ 40-DIP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:AVR® ATmega 标准包装:9 系列:87C 核心处理器:8051 芯体尺寸:8-位 速度:40/20MHz 连通性:UART/USART 外围设备:POR,WDT 输入/输出数:32 程序存储器容量:32KB(32K x 8) 程序存储器类型:OTP EEPROM 大小:- RAM 容量:256 x 8 电压 - 电源 (Vcc/Vdd):4.5 V ~ 5.5 V 数据转换器:- 振荡器型:内部 工作温度:0°C ~ 70°C 封装/外壳:40-DIP(0.600",15.24mm) 包装:管件